List of Super NES enhancement chips

The list of Super NES enhancement chips demonstrates the overall design plan for the Super Nintendo Entertainment System, whereby the console's hardware designers had made it easy to interface special coprocessor chips to the console. This standardized selection of chips was available to increase system performance and features for each game cartridge. As increasingly superior chips became available throughout the SNES's vintage market years, this strategy originally provided a cheaper and more versatile way of maintaining the system's market lifespan when compared to Nintendo's option of having included a much more expensive CPU or a more obsolete stock chipset.

As a result, various enhancement chips were integrated into the cartridges of select game titles. The presence of an enhancement chip is most often indicated by 16 additional pins on either side of the original pins, 8 to each side.[1]

Super FX

The Super FX chip is a 16-bit supplemental RISC CPU developed by Argonaut Games that was included in certain game cartridges to perform functions that the main CPU can not feasibly do.[2] It is typically programmed to act as a graphics accelerator chip that draws polygons to a frame buffer in the RAM sitting adjacent to it.

In addition to rendering polygons, the chip is also used to assist the SNES in rendering advanced 2D effects. Super Mario World 2: Yoshi's Island uses it for advanced graphics effects like sprite scaling and stretching, huge sprites that allow for boss characters to take up the whole screen, and multiple foreground and background parallax layers to give a greater illusion of depth.

This chip went through at least four revisions, first starting out as a surface mounted chip labeled "MARIO CHIP 1" (Mathematical, Argonaut, Rotation & I/O) in the earliest Star Fox cartridges, commonly called the Super FX. The following year, some boards were providing an epoxy version of it, and later a first revision came out under the label "GSU-1". Both versions are clocked with a 21 MHz signal, but an internal clock speed divider halves it to 10.5 MHz on the MARIO CHIP 1. The GSU-1 however runs at the full 21 MHz. Both the MARIO CHIP 1 and the GSU-1 can support a maximum ROM size of 8 Mbits. Later on, the design was revised to become the GSU-2, which is still 16-bit, but unlike the earlier Super FX chips, this version can support a ROM size greater than 8 MBit. The final known revision is the GSU-2-SP1. All versions of the Super FX chip are functionally compatible in terms of their instruction set. The differences arise in how they are packaged, their pinout, their maximum supported ROM size, and their internal clock speed.[3]

Cx4

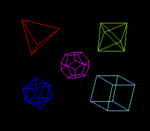

The Cx4 chip is a math coprocessor that was used by Capcom to perform general trigonometric calculations for wireframe effects, sprite positioning and rotation. It is known for its role in mapping and transforming wireframes in Capcom's second and third Mega Man X series games.[2] It is based on the Hitachi HG51B169 DSP.

A Cx4 self-test screen can be accessed by holding the 'B' button on the second controller upon system start-up in both Mega Man X2 and Mega Man X3.[4] In both the PlayStation 2 and Nintendo GameCube versions of Mega Man X Collection, this self-test screen is still accessible in Mega Man X2 (although differently accessed due to the remapped controller configuration), but not in Mega Man X3, because Mega Man X Collection features the 32-bit CD version of the game and not the SNES version.

DSP

This series of fixed-point digital signal processor chips allowed for fast vector-based calculations, bitmap conversions, both 2D and 3D coordinate transformations, and other functions.[5] Four revisions of the chip exist, each physically identical but with different microcode. The DSP-1 version, including the later 1A die shrink and 1B bug fix revisions, was most often used; the DSP-2, DSP-3, and DSP-4 were used in only one title each.[6] All of them are based on the NEC µPD77C25 CPU.

DSP-1

The DSP-1 is the most varied and widely used of the SNES DSPs, appearing in over 15 separate titles. It is used as a math coprocessor in games such as Super Mario Kart and Pilotwings that require more advanced Mode 7 scaling and rotation. It also provides fast support for the floating point and trigonometric calculations needed by 3D math algorithms. The later DSP-1A and DSP-1B serve the same purpose as the DSP-1. The DSP-1A is a die shrink of the DSP-1, and the DSP-1B also corrects several bugs.[7]

DSP-2

The DSP-2 can only be found in the SNES port of Dungeon Master. Its primary purpose is to convert Atari ST bitmap image data into the SNES bitplane format. It also provides dynamic scaling capability and transparency effects.

DSP-3

DSP-3 is an assistant chip, used in only one game for the Japanese Super Famicom, a turn-based strategy game titled SD Gundam GX. The chip assists with tasks like calculating the next AI move, Shannon-Fano bitstream decompression, and bitplane conversion of graphics.

DSP-4

DSP-4 is used in only one game cartridge, Top Gear 3000. It primarily assists with drawing the race track, especially during the times that the track branches into multiple paths.

GB-Z80

The chip inside the Super Game Boy peripheral possesses a core identical to the Z80-derived CPU in the handheld Game Boy. Because the Super NES is not powerful enough for software emulation of the Game Boy, circuitry equivalent to the entire handheld console is inside of the cartridge.[8]

MX15001TFC

This chip was made by MegaChips exclusively for Nintendo Power cartridges for the Super Famicom. The cartridges are equipped with flash ROMs instead of mask ROMs, and were designed to hold games downloaded for a fee from specialized kiosks in Japan. The chip manages communication with the kiosks to download ROM images, and provides an initial menu to select which of the downloaded games would be played. Some titles were produced both in cartridge and download form, while others were download only. The service was closed on February 8, 2007.[9]

OBC-1

OBC-1 is a sprite manipulation chip used exclusively in the Super Scope game Metal Combat: Falcon's Revenge, the sequel to Battle Clash.[2]

S-DD1

The S-DD1 chip is an ASIC decompressor made by Nintendo for use in some Super Nintendo Entertainment System Game Paks.[2] Designed to handle data compressed by ABS Lossless Entropy Algorithm, a form of arithmetic coding developed by Ricoh, its use is necessary in games where massive amounts of sprite data are compressed with a total design limit of 32-megabits. This data is decompressed dynamically by the S-DD1 and given directly to the picture processing unit.

The S-DD1 mediates between the Super NES's Ricoh 5A22 CPU and the game's ROM via two buses. However, the controlling 5A22 processor may still request normal, uncompressed data from the game's ROM even if the S-DD1 is already busy with a decompression operation. This form of parallelism allows sprite data to be decompressed while other types of data are quickly passed to the main CPU.

Star Ocean and Street Fighter Alpha 2 are the only games that use this chip. Emulation of the S-DD1 initially proved to be difficult, requiring "graphics packs" to be provided for the affected titles, until the compression algorithm was identified.[10][11]

S-RTC

S-RTC is a real-time clock chip used in one game, Daikaijuu Monogatari II.[2]

SA1

The Super Accelerator 1 (SA1) chip is used in a number of SNES games, including the popular Super Mario RPG: Legend of the Seven Stars.[12]

Similar to the 5A22 CPU in the SNES console, the SA1 contains a processor core based on the 65C816 with several programmable timers.[2] The SA1 does not function as a slave CPU for the 5A22; both can interrupt each other independently.

The SA1 also features a range of enhancements over the standard 65C816:

- Upgraded 10.74 MHz clock speed, up from a maximum of 3.58 MHz

- Faster RAM, including 2KBytes of internal RAM

- Memory mapping capabilities

- Limited data storage and compression

- New DMA modes such as bitmap to bit plane transfer

- Arithmetic functions (multiplication, division, and cumulative)

- Hardware timer (either as a linear 18-bit timer, or synchronised with the PPU to generate an IRQ at a specific H/V scanline location)

- Built-in CIC lockout, for copy protection and regional marketing control

SPC7110

A data decompression chip designed by Epson that is used in a few games by Hudson. Tengai Makyou Zero also contains a real-time clock chip accessed via the SPC7110.[2]

ST

The ST series of chips are used by SETA Corporation to enhance AI functionality.

ST010

Used for general functions and handling the AI of opponent cars in F1 ROC II: Race of Champions. Contains a NEC µPD96050 CPU.[7][13]

ST011

ST011 is used for AI functionality in the shogi board game Hayazashi Nidan Morita Shogi. It also uses a NEC µPD96050.[8]

ST018

ST018 is used for AI functionality in Hayazashi Nidan Morita Shogi 2. It is a 21.47 MHz, 32-bit ARMv3 processor.[7]

List of Super NES games that use enhancement chips

Cancelled games

| Title | Chip | Year | Developer | Publisher |

|---|---|---|---|---|

| Star Fox 2 | Super FX GSU-2 | - | Nintendo EAD | Nintendo |

| FX Fighter | Super FX GSU-2 | - | Argonaut Games | GTE Entertainment (NA) (EU) |

| Comanche | Super FX GSU-2 | - | Nova Logic | Nova Logic (NA) |

| Powerslide | Super FX GSU-1 | - | Elite Systems | Elite Systems (EU) |

References

- ↑ "Anomie's SNES Port Doc". Retrieved 2011-04-05.

- 1 2 3 4 5 6 7 (2007-05-01) Snes9x readme.txt v1.51. snes9x.com. Retrieved on 2007-07-03.

- ↑ "The Super FX chip". MyPSP News.

- ↑ "CX4 test functions and source code contributors".

- ↑ "Digital Signal Processing". Overload's Puzzle Sheet. 2006-05-29. Retrieved 2007-05-09.

- ↑ Nach; Moe, Lord Nightmare. "SNES Add-on Chip information". Retrieved 2007-05-09.

- 1 2 3 Byuu. "SNES Coprocessors — The Future Has Arrived". Archived from the original on 2012-03-07.

- 1 2 "ZSNES v1.51 Documentation". Retrieved 2007-07-03.

- ↑ "Nintendo Power". N-Sider.com. Retrieved 2007-07-03.

- ↑ "SNES9x Developers Journal (November 2000)". Retrieved 2014-09-07.

- ↑ "SNES9x Developers Journal (August 2003)". Retrieved 2014-09-07.

- ↑ "SA1 Demonstration Program". SNES Central.

- ↑ "ST-0010". Overload's Puzzle Sheet. Retrieved 2007-07-03.

See also

- Memory management controller are different kinds of special chips designed by various video game developers for use in Nintendo Entertainment System (NES) cartridges.