Intel 80386

Intel 80386 DX rated at 16 MHz | |

| Produced | From June 1986 to September 2007 |

|---|---|

| Common manufacturer(s) |

|

| Max. CPU clock rate | 12 MHz to 40 MHz |

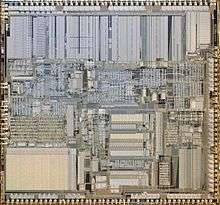

| Min. feature size | 1.5µm to 1µm |

| Instruction set | x86 (IA-32) |

| Predecessor | Intel 80286 |

| Successor | Intel 80486 |

| Package(s) | |

The Intel 80386 ("eight-oh-three-eighty-six"), also known as i386 or just 386, is a 32-bit microprocessor introduced in 1985.[1] The first versions had 275,000 transistors[2] and were the CPU of many workstations and high-end personal computers of the time. As the original implementation of the 32-bit extension of the 80286 architecture,[3] the 80386 instruction set, programming model, and binary encodings are still the common denominator for all 32-bit x86 processors, which is termed the i386-architecture, x86, or IA-32, depending on context.

The 32-bit 80386 can correctly execute most code intended for the earlier 16-bit processors such as 8088 and 80286 that were ubiquitous in early PCs. (Following the same tradition, modern 64-bit x86 processors are able to run most programs written for older x86 CPUs, all the way back to the original 16-bit 8086 of 1978.) Over the years, successively newer implementations of the same architecture have become several hundreds of times faster than the original 80386 (and thousands of times faster than the 8086).[4] A 33 MHz 80386 was reportedly measured to operate at about 11.4 MIPS.[5]

The 80386 was introduced in October 1985, while manufacturing of the chips in significant quantities commenced in June 1986.[6][7] Mainboards for 80386-based computer systems were cumbersome and expensive at first, but manufacturing was rationalized upon the 80386's mainstream adoption. The first personal computer to make use of the 80386 was designed and manufactured by Compaq[8] and marked the first time a fundamental component in the IBM PC compatible de facto-standard was updated by a company other than IBM.

In May 2006, Intel announced that 80386 production would stop at the end of September 2007.[9] Although it had long been obsolete as a personal computer CPU, Intel and others had continued making the chip for embedded systems. Such systems using an 80386 or one of many derivatives are common in aerospace technology and electronic musical instruments, among others. Some mobile phones also used (later fully static CMOS variants of) the 80386 processor, such as BlackBerry 950[10] and Nokia 9000 Communicator.

Architecture

| Intel 80386 registers | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

The processor was a significant evolution in the x86 architecture, and extended a long line of processors that stretched back to the Intel 8008. The predecessor of the 80386 was the Intel 80286, a 16-bit processor with a segment-based memory management and protection system. The 80386 added a 32-bit architecture and a paging translation unit, which made it much easier to implement operating systems that used virtual memory. It also offered support for register debugging.

The 80386 featured three operating modes: real mode, protected mode and virtual mode. The protected mode which debuted in the 286 was extended to allow the 386 to address up to 4 GB of memory. The all new virtual 8086 mode (or VM86) made it possible to run one or more real mode programs in a protected environment, although some programs were not compatible.

The ability for a 386 to be set up to act like it had a flat memory model in protected mode despite the fact that it uses a segmented memory model in all modes would arguably be the most important feature change for the x86 processor family until AMD released x86-64 in 2003.

Several new instructions have been added to 386: BSF, BSR, BT, BTS, BTR, BTC, CDQ, CWDE, LFS, LGS, LSS, MOVSX, MOVZX, SETcc, SHLD, SHRD.

Two new segment registers have been added (FS and GS) for general purpose programs, single Machine Status Word of 286 grew into eight control registers CR0-CR7. Debug registers DR0-DR7 were added for hardware breakpoints. New forms of MOV instruction are used to access them.

Chief architect in the development of the 80386 was John H. Crawford.[11] He was responsible for extending the 80286 architecture and instruction set to 32-bit, and then led the microprogram development for the 80386 chip.

The 80486 and P5 Pentium line of processors were descendants of the 80386 design.

Datatypes of 80386

The following data types are directly supported and thus implemented by one or more 80386 machine instructions; these data types are described here in brief. (source:,[12] page 514):

- Bit (boolean value), bit field (group of up to 32 bits) and bit string (up to 4Gb in length).

- 8-bit integer (byte), either signed (range −128..127) or unsigned (range 0..255).

- 16-bit integer, either signed (range −32,768..32,767) or unsigned (range 0..65,535).

- 32-bit integer, either signed (range −231..231−1) or unsigned (range 0..232−1).

- 64-bit integer, either signed (range −263..263−1) or unsigned (range 0..264−1).

- Offset, a 16 or 32-bit displacement referring to a memory location (using any addressing mode).

- Pointer, a 16-bit selector together with a 16 or 32 bit offset.

- Character (8-bit character code).

- String, a sequence of 8, 16 or 32-bit words (up to 4 Gb in length).

- BCD, decimal digits (0..9) represented by unpacked bytes.

- Packed BCD, two BCD digits in one byte (range 0..99).

Example code

The following 80386 assembly source code is for a subroutine named _strtolower that copies a null-terminated ASCIIZ character string from one location to another, converting all alphabetic characters to lower case. The string is copied one byte (8-bit character) at a time.

0000

0000 55

0001 89 E5

0003 8B 75 0C

0006 8B 7D 08

0009 8A 06

000B 46

000C 3C 41

000E 0F 8C FC FF FF FF

0014 3C 5A

0016 0F 8F FC FF FF FF

001C 04 20

001E 88 07

0020 47

0021 3C 00

0023 0F 85 FC FF FF FF

0029 5D

002A C3

002B

|

; _strtolower:

; Copy a null-terminated ASCII string, converting

; all alphabetic characters to lower case.

;

; Entry stack parameters

; [ESP+8] = src, Address of source string

; [ESP+4] = dst, Address of target string

; [ESP+0] = Return address

;

_strtolower proc

push ebp ;Set up the call frame

mov ebp,esp

mov esi,[ebp+12] ;Set ESI = src

mov edi,[ebp+8] ;Set EDI = dst

loop mov al,[esi] ;Load AL from [src]

inc esi ;Increment src

cmp al,'A' ;If AL < 'A',

jl copy ; Skip conversion

cmp al,'Z' ;If AL > 'Z',

jg copy ; Skip conversion

add al,'a'-'A' ;Convert AL to lowercase

copy mov [edi],al ;Store AL to [dst]

inc edi ;Increment dst

cmp al,0 ;If AL<>0,

jne loop ; Repeat the loop

done pop ebp ;Restore the prev call frame

ret ;Return to caller

end proc

|

The example code uses the EBP (base pointer) register to establish a call frame, an area on the stack that contains all of the parameters and local variables for the execution of the subroutine. This kind of calling convention supports reentrant and recursive code, and has been used by Algol-like languages since the late 1950s. A flat memory model is assumed, specifically, that the DS and ES segments address the same region of memory.

Chip variants

The 80386SX variant

In 1988, Intel introduced the 80386SX, most often referred to as the 386SX, a cut-down version of the 80386 with a 16-bit data bus mainly intended for lower cost PCs aimed at the home, educational, and small business markets while the 386DX would remain the high end variant used in workstations, servers, and other demanding tasks. The CPU remained fully 32-bit internally, but the 16-bit bus was intended to simplify circuit board layout and reduce total cost.[13] The 16-bit bus simplified designs but hampered performance. Only 24 pins were connected to the address bus, therefore limiting addressing to 16 MB,[14] but this was not a critical constraint at the time. Performance differences were due not only to differing data bus-widths, but also due to performance-enhancing cache memories often employed on boards using the original chip.

The original 80386 was subsequently renamed 80386DX to avoid confusion. However, Intel subsequently used the 'DX' suffix to refer to the floating-point capability of the 80486DX. The 80387SX was an 80387 part that was compatible with the 386SX (i.e. with a 16-bit databus). The 386SX was packaged in a surface-mount QFP, and sometimes offered in a socket to allow for an upgrade.

The i386SL variant

The i386SL was introduced as a power efficient version for laptop computers. The processor offered several power management options (e.g. SMM), as well as different "sleep" modes to conserve battery power. It also contained support for an external cache of 16 to 64 kB. The extra functions and circuit implementation techniques caused this variant to have over 3 times as many transistors as the i386DX. The i386SL was first available at 20 MHz clock speed,[15] with the 25 MHz model later added.[16]

Business importance

The first company to design and manufacture a PC based on the Intel 80386 was Compaq. By extending the 16/24-bit IBM PC/AT standard into a natively 32-bit computing environment, Compaq became the first third party to implement a major technical hardware advance on the PC platform. IBM was offered use of the 80386, but had manufacturing rights for the earlier 80286. IBM therefore chose to rely on that processor for a couple more years. The early success of the Compaq 386 PC played an important role in legitimizing the PC "clone" industry, and in de-emphasizing IBM's role within it.

Prior to the 386, the difficulty of manufacturing microchips and the uncertainty of reliable supply made it desirable that any mass-market semiconductor be multi-sourced, that is, made by two or more manufacturers, the second and subsequent companies manufacturing under license from the originating company. The 386 was for a time (4.7 yrs) only available from Intel, since Andy Grove, Intel's CEO at the time, made the decision not to encourage other manufacturers to produce the processor as second sources. This decision was ultimately crucial to Intel's success in the market. The 386 was the first significant microprocessor to be single-sourced. Single-sourcing the 386 allowed Intel greater control over its development and substantially greater profits in later years.

AMD introduced its compatible Am386 processor in March 1991 after overcoming legal obstacles, thus ending Intel's 4.7 yr monopoly on 386-compatible processors. From 1991 IBM also manufactured 386 chips under license for use only in IBM PCs and boards.

Compatibles

- The AMD Am386SX and Am386DX were almost exact clones of the 80386SX and 80386DX. Legal disputes caused production delays for several years, but AMD's 40 MHz part eventually became very popular with computer enthusiasts as a low cost and low power alternative to the 25 MHz 486SX. The power draw was further reduced in the "notebook models" (Am386 DXL/SXL/DXLV/SXLV) which could operate with 3.3V and were implemented in fully static CMOS circuitry.

- Chips and Technologies Super386 38600SX and 38600DX were developed using reverse engineering. They sold poorly, due to some technical errors and incompatibilities, as well as their late appearance on the market. They were therefore short-lived products.

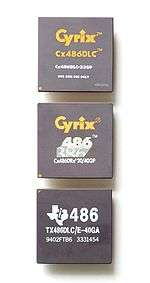

- Cyrix Cx486SLC/Cx486DLC could be (simplistically) described as a kind of 386/486 hybrid chip that included a small amount of on-chip cache. It was popular among computer enthusiasts but did poorly with OEMs. The Cyrix Cx486SLC and Cyrix Cx486DLC processors were pin-compatible with 80386SX and 80386DX respectively. These processors were also manufactured and sold by Texas Instruments.

- IBM 386SLC and 486SLC/DLC were variants of Intel's design which contained a large amount of on-chip cache (8 kB, and later 16 kB). The agreement with Intel limited their use to IBM's own line of computers and upgrade boards only, so they were not available on the open market.

Early problems

Intel originally intended for the 80386 to debut at 16 MHz. However, due to poor yields, it was instead introduced at 12 MHz.

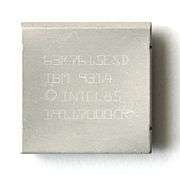

Early in production, Intel discovered a marginal circuit that could cause a system to return incorrect results from 32-bit multiply operations. Not all of the processors already manufactured were affected, so Intel tested its inventory. Processors that were found to be bug-free were marked with a double-sigma (ΣΣ), and affected processors were marked "16 BIT S/W ONLY". These latter processors were sold as good parts, since at the time 32 bit capability was not relevant for most users. Such chips are now extremely rare.

The i387 math coprocessor was not ready in time for the introduction of the 80386, and so many of the early 80386 motherboards instead provided a socket and hardware logic to make use of an 80287. In this configuration the FPU would operate asynchronously to the CPU, usually with a clock rate of 10 MHz. The original Compaq Deskpro 386 is an example of such design. However, this was an annoyance to those who depended on floating point performance, as the performance advantages of the 80387 over the 80287 were significant.

Pin-compatible upgrades

Intel later offered a modified version of its 80486DX in 80386 packaging, branded as the Intel RapidCAD. This provided an upgrade path for users with 80386-compatible hardware. The upgrade was a pair of chips that replaced both the 80386 and 80387. Since the 80486DX design contained an FPU, the chip that replaced the 80386 contained the floating point functionality, and the chip that replaced the 80387 served very little purpose. However, the latter chip was necessary in order to provide the FERR signal to the mainboard and appear to function as a normal floating point unit. The CAD branding referred to the ease of upgrading existing OEM designs from 386 to 486 CPUs with rapid turn-around in the CAD room.

Third parties offered a wide range of upgrades, for both SX and DX systems. The most popular ones were based on the Cyrix 486DLC/SLC core, which typically offered a substantial speed improvement due to its more efficient instruction pipeline and internal L1 SRAM cache. The cache was usually 1 kB, or sometimes 8 kB in the TI variant. Some of these upgrade chips (such as the 486DRx2/SRx2) were marketed by Cyrix themselves, but they were more commonly found in kits offered by upgrade specialists such as Kingston, Evergreen and Improve-It Technologies. Some of the fastest CPU upgrade modules featured the IBM SLC/DLC family (notable for its 16 kB L1 cache), or even the Intel 486 itself. Many 386 upgrade kits were advertised as being simple drop-in replacements, but often required complicated software to control the cache or clock doubling. Part of the problem was that on most 386 motherboards, the A20 line was controlled entirely by the motherboard with the CPU being unaware, which caused problems on CPUs with internal caches.

Overall it was very difficult to configure upgrades to produce the results advertised on the packaging, and upgrades were often less than 100% stable or less than 100% compatible.

Models and variants

Early 5 V models

80386DX

Original version, released in October 1985.

- Capable of working with 16- or 32-bit external busses

- Cache: depends on mainboard

- Package: PGA-132 or PQFP-132

- Process: First types CHMOS III, 1.5 µm, later CHMOS IV, 1 µm

- Die size: 104 mm² (ca. 10 mm x 10 mm) in CHMOS III and 39 mm² (6 mm x 6.5 mm) in CHMOS IV.

- Transistor count: 275,000[2]

- Specified max clock: 12 MHz (early models), later 16, 20, 25 and 33 MHz

RapidCAD

A specially packaged Intel 486DX and a dummy floating point unit (FPU) designed as pin-compatible replacements for an Intel 80386 processor and 80387 FPU.

Versions for embedded systems

80376

This was an embedded version of the 80386SX which did not support real mode and paging in the MMU.

i386EX, i386EXTB and i386EXTC

System and power management and built in peripheral and support functions: Two 82C59A interrupt controllers; Timer, Counter (3 channels); Asynchronous SIO (2 channels); Synchronous SIO (1 channel); Watchdog timer (Hardware/Software); PIO. Usable with 80387SX or i387SL FPUs.

- Data/address bus: 16 / 26 bits

- Package: PQFP-132, SQFP-144 and PGA-168

- Process: CHMOS V, 0.8 µm

- Specified max clock:

- i386EX: 16 MHz @2.7~3.3 volt or 20 MHz @3.0~3.6 volt or 25 MHz @4.5~5.5 volt

- i386EXTB: 20 MHz @2.7~3.6 volt or 25 MHz @3.0~3.6 volt

- i386EXTC: 25 MHz @4.5~5.5 volt or 33 MHz @4.5~5.5 volt

i386CXSA and i386SXSA (or i386SXTA)

Transparent power management mode, integrated MMU and TTL compatible inputs (only 386SXSA). Usable with i387SX or i387SL FPUs.

- Data/address bus: 16 / 26 bits (24 bits for i386SXSA)

- Package: PQFP-100

- Voltage: 4.5~5.5 volt (25 and 33 MHz); 4.75~5.25 volt (40 MHz)

- Process: CHMOS V, 0.8 µm

- Specified max clock: 25, 33, 40 MHz

i386CXSB

Transparent power management mode and integrated MMU. Usable with i387SX or i387SL FPUs.

- Data/address bus: 16 / 26 bits

- Package: PQFP-100

- Voltage: 3.0 volt (16 MHz) or 3.3 volt (25 MHz)

- Process: CHMOS V, 0.8 µm

- Specified max clock: 16, 25 MHz

Notes and references

- ↑ More precise: The 80386 architecture was presented in detail in 1984. Samples were produced in 1985 (possibly late 1984) with mass production and delivery of a final version starting in June 1986.

- 1 2 mit.edu—The Future of FPGAs (Cornell) 2012-10-11

- ↑ Which itself was an extension of the 8086-architecture with advanced memory management functions and significantly better performance.

- ↑ Not counting the advances in the performance of corresponding x87 implementations. These are measured in tens of thousands of times, compared to the original 8087, or hundreds of thousands of times compared to software implementations of floating point on the 8086.

- ↑ Intel 80386

- ↑ Forbes, Jim (January 27, 1986). "Development of 386 Accelerating". InfoWorld. Vol. 8 no. 4. InfoWorld Media Group. p. 5. ISSN 0199-6649.Introduced October 1985, production chip in June 1986

- ↑ Ranney, Elizabeth (September 1, 1986). "ALR Hopes to Beat Completion With Fall Release of 386 Line". InfoWorld. Vol. 8 no. 35. InfoWorld Media Group. p. 5. ISSN 0199-6649.First 80386 computers released around October 1986

- ↑ http://web.archive.org/web/20090627055110/http://www.crn.com/crn/special/supplement/816/816p65_hof.jhtml

- ↑ "Intel cashes in ancient chips".

- ↑ http://the-gadgeteer.com/2001/02/26/rim_blackberry_950_review/

- ↑ "Intel Fellow—John H. Crawford". Intel.com. 2010-08-16. Retrieved 2010-09-17.

- ↑ A K Ray, K M Bhurchandi, “Advanced microprocessors and peripherals”

- ↑ This was a similar approach to that used by Intel with the 8088, a derivative of the Intel 8086, that was used in the original IBM PC.

- ↑ The 16 MB limit was similar to that of the 68000, a comparable processor.

- ↑ "Chronology of Microprocessors (1990-1992)". Islandnet.com. Retrieved 2010-09-17.

- ↑ Mueller, Scott. "Microprocessor Types and Specifications > P3 (386) Third-Generation Processors". InformIT. Retrieved 2010-09-17.

External links

- Intel 80386 Programmer's Reference Manual 1986 (PDF)

- Intel 80386 processor family

- Intel 231746-001 Introduction to the 80386 Apr86 (April 1986) and Including the 80386 Data Sheet Intel 231630-002 80386 HIGH PERFORMANCE 32-BIT MICROPROCESSOR WITH INTEGRATED MEMORY MANAGEMENT—Data Sheet for 80386-12 and 80386-16

- 1988 Intel Microprocessors and Peripheral Handbook Volume 1 Microprocessor including 80386 HIGH PERFORMANCE 32-BIT CHMOS MICROPROCESSOR WITH INTEGRATED MEMORY MANAGEMENT October 1987 Order Number: 231630-004

- 1989 Intel Microprocessor and Peripheral Handbook Vol 1 Microprocessor including 386™ MICROPROCESSOR HIGH PERFORMANCE 32-BIT CHMOS MICROPROCESSOR WITH INTEGRATED MEMORY MANAGEMENT November 1988 Order Number: 231630-005

- Detailed list of early 80386 steppings (revisions)